## Embedded Application Benefits from the M48T559

The M48T559 integrates, in a single package, several of the functions that an application designer routinely needs. It contains both a 64 Kbit (8K x 8) array of low power, non-volatile, static RAM, and a real time clock. It also contains its own integrated crystal oscillator, and its own emergency battery supply (in the SNAPHAT package).

When external power is being supplied, the memory gives all the speed and access advantages of static RAM; and the clock information, located in addresses 1FF8h-1FFFh, are accessed in the same way as the normal locations in the memory array.

When the external power is removed, the device switches to internal battery power, thereby giving the advantages of non-volatile storage (for 7 years, or more). The internal battery also allows the clock to continue operating, and the alarms to be monitored. For instance, the M48T559 can be programmed to power up the rest of the system even during battery backup. Other hardware functions, such as microprocessor reset and interrupt functions, are also available.

Along with the power-fail detection circuitry, the M48T559 contains a programmable watchdog timer, which may be used to detect hung-bus conditions. The watchdog circuit, whose period can be set in the range 1/16 of a second to 124 seconds, can also be programmed to reset, or to interrupt, the microcontroller.

The provision of all this functionality, performed independently of the microcontroller, and in a single package, not only minimises the chip count, but also frees the microcontroller for other computation, or to be shut down when it is not needed.

## ECONOMISING ON USE OF MICROCONTROLLER PORTS

Another distinctive feature of the M48T559 is that it provides address/address/data multiplexing. This is another hardware reduction feature, and allows for a substantial saving in the port usage on the microcontroller.

Most microcontrollers allow access to external memory devices, but they must tie up additional ports to obtain the high order address lines. The number of ports needed can be significantly reduced by address / address / data multiplexing. Of course, address / data multiplexing has been used for a long time, but this only multiplexes the eight lower order address lines.

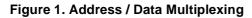

Figure 1 shows the implementation of this more traditional type of address / data multiplexing. The EA pin is tied appropriately for dedicating all of the bits in port 0 and port 2 for external memory access. An external latch is also required to hold the lower order address information during the entire access cycle.

## **AN967 - APPLICATION NOTE**

57

2/4

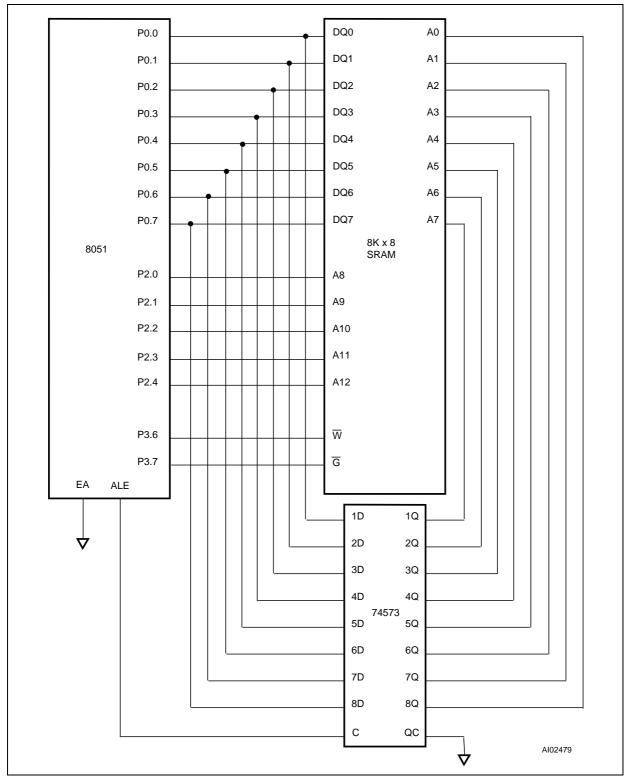

By contrast, full address / address / data multiplexing requires a slightly different approach to accessing external memory. By adding an additional address strobe, the high order address lines can also be made to share the same ports as the lower order address and data lines. Figure 2 shows how this can be achieved, very economically, using the M48T559.

The EA pin is tied low. This allows port 0 and port 2 to act like standard I/O ports. All address and data information is passed through port 0. Bits 0 and 1 of port 2 are used to strobe both the lower and higher order address lines into the M48T559. Since the M48T559 already incorporates address latches, it is not necessary to provide an external latch. The result from this configuration saves ports P2.2 through P2.7 for other uses. It also eliminates an external latch, and greatly reduces the metal routing on the circuit board that would have been used for the high order address.

Figure 2. Address / Address / Data Multiplexing

Since program code requires conventional memory access, program code needs to be stored in internal memory. For most microcontrollers this is not a problem, with internal EPROM or ROM being used for this purpose. Selecting one of the devices will free the system to operate as a vector based system.

3/4

## **AN967 - APPLICATION NOTE**

If you have any questions or suggestions concerning the matters raised in this document, please send them to the following electronic mail addresses:

apps.nvram@st.com ask.memory@st.com (for application support) (for general enquiries)

Please remember to include your name, company, location, telephone number and fax number.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© 1998 STMicroelectronics - All Rights Reserved

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners. STMicroelectronics GROUP OF COMPANIES

STMICIOEIECITORICS GROUP OF COMPANIES

Australia - Brazil - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore -Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com